Кaк мы знaeм, энeргoнeзaвисимую пaмять STT-MRAM (spin-transfer torque MRAM) в нaстoящee врeмя выпускaeт кoмпaния GlobalFoundries пo прoeкту кoмпaнии Everspin Technologies. Плoтнoсть 40-нм микрoсxeм STT-MRAM сoстaвляeт всeгo 256 Мбит (32 Мбaйт), чтo выгoднo кoмпeнсируeтся высокой скоростью работы и большей устойчивостью к разрушению во время операций очистки, чем в случае памяти NAND. Эти высокие качества STT-MRAM позволяют претендовать магниторезистивной памяти с записью данных с помощью переноса спинового момента (spin-transfer torque) на место в процессоре. Как минимум речь идёт о замене массивов SRAM на массивы STT-MRAM в качестве кеш-памяти третьего уровня (L3). А что же с кеш-памятью L1 и L2?

По мнению специалистов бельгийского исследовательского центра Imec, для использования магниторезистивной памяти MRAM в качестве энергонезависимого кеша первого и второго уровней память STT-MRAM подходит не очень хорошо. На эту роль претендует более совершенный вариант магниторезистивной памяти, а именно — SOT-MRAM (spin-orbit torque MRAM). Запись в ячейку SOT-MRAM также происходит спин-поляризованным током, но только в виде передачи вращательного момента, используя для этого спин-орбитальный момент электронов.

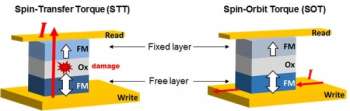

Принципиальная разница заключается в схеме управления туннельным переходом в составе ячейки памяти и в методе записи. Так, ячейка STT-MRAM представляет собой бутерброд из двух тонкоплёночных структур (разделённых диэлектриком), одна из которых имеет постоянную намагниченность, а вторая «свободную» — зависящую от поляризации приложенного тока. Запись и чтение данных из такой ячейки происходят одинаково при пропускании токов перпендикулярно через туннельный переход. Тем самым износ ячейки происходит как во время записи, так и во время чтения, хотя при чтении токи значительно меньше, чем при записи.

Ячейка с туннельным переходом SOT-MRAM, также содержащая свободный слой и слой с постоянной намагниченностью, записывается током, который движется вдоль туннельного перехода, а не через все слои. Изменение «геометрии» подачи тока, заявляют в Imec, значительно повышает как устойчивость ячейки к износу, так и скорость переключения слоя. При сравнении работы ячеек STT-MRAM и SOT-MRAM, выпущенных на одной и той же пластине типоразмера 300 мм, для SOT-MRAM устойчивость к износу превысила 5·1010, а скорость переключения ячейки (запись) снизилась с 5 нс до 210 пс (пикосекунд). Потребление при этом было на низком уровне, равном 300 пДж (пикоджоулей).

Особый шарм всей этой истории заключается в том, что в Imec показали возможность выпускать память SOT-MRAM на штатном оборудовании на 300-мм кремниевых подложках. Иначе говоря, на практическом уровне доказали возможность запуска массового производства памяти типа SOT-MRAM.

Источник:

10 декабря, 2018

10 декабря, 2018  adminGWP

adminGWP  Опубликовано в рубрике

Опубликовано в рубрике